ELSEVIER

#### Contents lists available at ScienceDirect

#### **Organic Electronics**

journal homepage: www.elsevier.com/locate/orgel

### Graphene-induced enhancement of charge carrier mobility and air stability in organic polythiophene field effect transistors

Gen-Wen Hsieh<sup>a,\*</sup>, Zong-Rong Lin<sup>a</sup>, Chun-Yi Hung<sup>a</sup>, Sheng-Yu Lin<sup>a</sup>, Chii-Rong Yang<sup>b</sup>

- a Institute of Lighting and Energy Photonics, National Chiao Tung University, 301, Gaofa 3rd Road, Guiren District, Tainan 71150, Taiwan, ROC

- b Department of Mechatronic Engineering, National Taiwan Normal University, 162, Section 1, Heping East Road, Taipei City 106, Taiwan, ROC

#### ARTICLE INFO

## Keywords: Air stability Charge carrier mobility Field effect transistor Graphene Polythiophene

#### ABSTRACT

We investigate multifunctional graphene nanostructures as charge carrier mobility enablers and moisture and air barrier films for organic-based polythiophene field effect transistors. Primary results show that a tiny amount of graphene flakes blended in the polythiophene active channel could reach a ten-fold increase in effective transistor mobility. Moreover, densely packed honeycomb graphene for efficient moisture and air shielding is firstly applied on organic active channels without any supporting polymer, resulting in mild mobility degradation in ambient environment with respect to unprotected polythiophene devices. Thus, hybrid graphene-polythiophene blend transistors laminated with graphene passivation layers exhibit significantly superior and prolonged performances over 1400 h, whereas the hybrid devices without graphene passivation become unswitchable in 600 h. Moreover, their low processing temperature (< 150 °C), solution processability, and flexibility of both graphene and polythiophene makes them a highly promising means for next-generation organic field effect transistors.

#### 1. Introduction

Graphene and other two-dimensional nanomaterials have attracted extensive attentions for both fundamental investigations and potential applications, ranging from biomedical and sensing, to energy and electronics, due to their fascinating optoelectronic, mechanical and physical characteristics [1–6]. Graphene has been regarded as an ideal transparent electrode candidate for flexible touch panels, organic light emitting diodes, thin film photovoltaics and organic field effect transistors (FETs) [7–12]. Recent advances further show that the sp²-hybridized carbon honeycomb framework of graphene can enable  $\pi$ - $\pi$  interactions with other organic and inorganic materials. Hence, different forms of graphene nanostructures, such as liquid phase exfoliated graphene [6,13], graphene nanoribbons [14], reduced graphene oxides [15], and graphene oxides [16], have been considered as a viable additive to organic polymeric or molecular matrices, with the hope of constituting hybrid architectures with augmentative performance.

Moreover, the need for high barrier encapsulation to active device components in organic optoelectronics is particularly demanding since moisture and air are the most detrimental and life-limiting factors. Toward this end, thin film encapsulation that can enable reduction in the weight and thickness of devices is the most popular means because conventional encapsulation based on rigid glass lid is inappropriate for

flexible devices. Though superior in resisting moisture and air, inorganic thin film insulating layers (e.g., SiNx, SiOx, AlOx) that are deposited by reactive sputtering, evaporation, or atomic layer deposition are generally opaque, non-flexible and costly [17-21]. Considerably, flexible and transparent graphene films could serve as an excellent barrier to gases because of their densely packed six-carbon ring framework and superior chemical stability [22]. To cover the large-area active region of an organic optoelectronic device, chemical vapor deposition (CVD)-grown graphene appears to be the promising candidate via various transfer printing methods. For instances, gas barrier properties of CVD-grown graphene films as a top electrode layer in organic photovoltaic devices have been investigated [23]. Laminating polymersupported graphene sheets as top passivation layers can extend device functionality in polymer light emitting diodes [24] and organic FETs [25]. However, there have been no reports of utilizing solitary graphene as gas barriers without any intermediate supporting film for organic active channels.

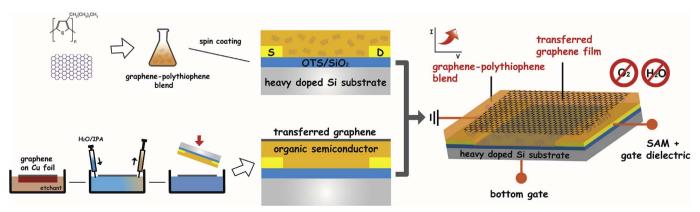

Here we describe a novel strategy for fabricating organic-based FETs with multifunctional graphene nanostructures that relies on (i) a solution-processed active channel containing graphene flakes and organic semiconducting polythiophene polymers, and (ii) an additive passivation layer of CVD graphene film atop transistor active channels. Our empirical results reveal that the loading of graphene in the active

E-mail address: cwh31@nctu.edu.tw (G.-W. Hsieh).

<sup>\*</sup> Corresponding author.

G.-W. Hsieh et al. Organic Electronics 54 (2018) 27–33

channel plays a crucial role in transistor performance. Effective field effect mobilities of graphene-polythiophene blend transistors are increased by a factor of more than ten compared to those of pristine polythiophene FETs. Moreover, the air stability tests based on graphene-protected polythiophene and graphene-protected hybrid graphene-polythiophene FETs are also investigated. It is found that the addition of CVD graphene film on the device surface can effectively alleviate the unfavorable polymer degradation due to the exposure of moisture and air in ambient air.

#### 2. Materials and methods

#### 2.1. Preparation of graphene-polythiophene blend solutions

Graphene dispersions were prepared by an adaptation of the solution sonication method [26]. Commercial purified graphene flakes (HGN-5, The-hydroxyl® Applied Carbon Technology) were dispersed in 1,2-dichlorobenzene (99%, ACROX) (initial tion = 5 mg mL<sup>-1</sup>). The well-dispersed graphene solution was produced by sonication in a bath (Delta, D150) (150 W, 43 kHz, 120 min), and subsequent centrifugation (Digisystem, SF-15B) (3000 rpm, 6 h). The top supernatant portion of the solution yielded a graphene dispersion containing single-to-few layer graphene flakes (with diameter of  $\sim 200-500$  nm); its concentration was about 0.065 mg mL<sup>-1</sup> (determined by ultraviolet-visible absorption spectroscopy). A proper amount of poly(3-hexylthiophene-2,5-diyl) (P3HT, Uni Region Bio-Tech) was then dissolved in the graphene (Gr) dispersions to prepare Gr-P3HT blends with different graphene loadings of 0, 0.4, 0.7, 1, 2, 5, and 10 wt%.

#### 2.2. Fabrication of graphene-polythiophene blend transistors

Bottom-gate bottom-contact FETs with a series of active channel layers comprising homogeneous blends of graphene flake and polythiophene semiconductor were fabricated. Source and drain contact patterns (Cr/Au: 5/50 nm thick) with channel length (L) of 10  $\mu$ m and width (W) of 500  $\mu$ m were defined by conventional photolithography, thermal evaporation and lift-off onto heavily doped n-type Si substrates with thermally grown SiO<sub>2</sub> (300 nm thick) as dielectric layers. The surfaces were then treated with hydrophobic self-assembled monolayers of 1-octyltrichlorosilane for better molecular stacking. Subsequently, a thin layer ( $\sim$ 100 nm thick) of Gr-P3HT blend solution was spin-coated onto the surface-treated substrates with patterned electrodes inside a N<sub>2</sub> glove box. Pristine P3HT devices were also preceded in the same manner. Finally, these Gr-P3HT blend and pristine P3HT devices were annealed (140 °C, 10 min) and naturally cooled down to room temperature inside a N<sub>2</sub> glove box.

#### 2.3. Direct polymer-free transfer of CVD graphene

Bilayer graphene was grown on copper (Cu) foils by a typical thermal atmospheric pressure chemical vapor deposition method [27,28]. Briefly, a Cu foil substrate (18  $\mu m$  thick, purity > 99.97%,  $O_2 < 10$  ppm, purchased from Landon Metal Co. Ltd, Taiwan) was electropolished and then loaded into a quartz tube and heated to 1020 °C under an argon atmosphere (550 sccm). The growth of graphene was then carried out by flowing  $H_2/CH_4/Ar$  (1/55/495 sccm) gas mixture for 5 min, and the sample was naturally cooled down to room temperature under a mixture flow of  $H_2/Ar$  (10/540 sccm). Bilayer structures appear to predominate in Raman spectrum for the as-grown graphene samples.

For graphene transfer, the as-grown graphene on Cu foil was back side polished and put in a petri dish (graphene side up) with 0.1 M Iron (III) chloride (FeCl<sub>3</sub>) etching solution. After copper was etched, the graphene film would float on the surface of the solution. The etchant was then gradually replaced by a mixture of water and 2-propanol (10:1) in the same petri dish, in order to reduce the surface tension of the solution [29]. The as-fabricated FET or bare SiO<sub>2</sub>/Si substrate was placed upside down above the floating graphene film and was then lowered onto the film with a tilting angle of  $\sim 30^\circ$ . Finally, the sample was heated at 60 °C for 15 min in  $N_2$  environment to dry the transferred graphene film. Note that this direct polymer-free transfer method provided a mean sheet resistance of 200  $\Omega$  per square for the transferred graphene film on SiO<sub>2</sub>/Si substrates. For comparison, poly(methyl methacrylate) (PMMA) was also used as a carrier material for CVD graphene transfer.

#### 2.4. Characterization of graphene-polythiophene transistors

The electrical measurements of these hybrid Gr-P3HT FETs, graphene-passivated FETs and pristine P3HT devices were carried out under ambient air at room temperature (23–25 °C, relative humidity ~50–60%) with dim light by a semiconductor device analyzer (Agilent 4155C) with a probe station. Transconductance ( $g_m$ ), threshold voltage ( $V_T$ ), and effective field effect mobility ( $\mu_{FE}$ ) of the FETs were extracted from the probed transfer characteristic ( $I_{DS}$  vs.  $V_{GS}$ ) by using the following general expressions governing the operation in the saturation regime [30]:

$$I_{DS,sat} = \frac{1}{2} \mu_{FE} C_i \frac{W}{L} (V_{GT} - V_T)^2, gm = \frac{\partial I_{DS,sat}}{\partial I_{GS}} = \mu_{FE} C_i \frac{W}{L} (V_{GS} - V_T)$$

(1)

where  $I_{DS}$  is the drain-source current,  $V_{GS}$  is the gate-source voltage,  $V_{DS}$  is the drain-source voltage,  $C_i$  is the gate dielectric capacitance per unit area, W is the channel width and L is the channel length.

Fig. 1. Schematic illustration of process flow for fabricating hybrid graphene-polythiophene blend FETs with an additive passivation layer of laminated CVD graphene sheet.

# دريافت فورى ب متن كامل مقاله

### ISIArticles مرجع مقالات تخصصی ایران

- ✔ امكان دانلود نسخه تمام متن مقالات انگليسي

- ✓ امكان دانلود نسخه ترجمه شده مقالات

- ✓ پذیرش سفارش ترجمه تخصصی

- ✓ امکان جستجو در آرشیو جامعی از صدها موضوع و هزاران مقاله

- ✓ امكان دانلود رايگان ۲ صفحه اول هر مقاله

- ✔ امکان پرداخت اینترنتی با کلیه کارت های عضو شتاب

- ✓ دانلود فوری مقاله پس از پرداخت آنلاین

- ✓ پشتیبانی کامل خرید با بهره مندی از سیستم هوشمند رهگیری سفارشات